#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

#### (19) World Intellectual Property **Organization**

International Bureau

(10) International Publication Number WO 2013/074373 Al

#### (43) International Publication Date 23 May 2013 (23.05.2013)

(51) International Patent Classification: B65G 49/07 (2006.01) **H01L 21/677** (2006.01) H05K 13/04 (2006.01) **B65G 47/91** (2006.01) H05K 13/02 (2006.01)

(21) International Application Number:

PCT/US20 12/064221

(22) International Filing Date:

8 November 2012 (08.1 1.2012)

(25) Filing Language: English

(26) Publication Language: **English**

(30) Priority Data:

| 61/561,706 | 18 November | 201 1 (18. 11.201 1) | US |

|------------|-------------|----------------------|----|

| 61/594,919 | 3 February  | 2012 (03.02.2012)    | US |

| 61/597,109 | 9 February  | 2012 (09.02.2012)    | us |

| 61/597,658 | 10 February | 2012 (10.02.2012)    | us |

| 13/372,422 | 13 February | 2012 (13.02.2012)    | us |

|            |             |                      |    |

- (71) Applicant: LUXVUE TECHNOLOGY CORPORATION TION [US/US]; 1705 Wyatt Drive, Santa Clara, CA 95054 (US).

- (72) Inventors: BIBL, Andreas; 588 Harrington Avenue, Los Altos, CA 94024 (US). HIGGINSON, John A.; 2826 Forbes Avenue, Santa Clara, CA 95051 (US). LAW, Hung-Fai Stephen; 1475 Montclaire Place, Los Altos, CA 94024 (US). HU, Hsin-Hua; 1489 Holt Avenue, Los Altos, CA 94024 (US).

- (74) Agents: VINCENT, Lester J. et al; Blakely, Sokoloff, Taylor & Zafhian LLP, 1279 Oakmead Parkway, Sunnyvale, CA 94085-4040 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) **Designated States** (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: MICRO DEVICE TRANSFER HEAD HEATER ASSEMBLY AND METHOD OF TRANSFERRING A MICRO **DEVICE**

fer head is heated to a temperature above the liquidus temperature of the bonding layer. Upon contacting the micro device with the transfer head, the heat from the transfer head transfers into the bonding layer to at least partially melt the bonding layer. A voltage applied to the transfer head creates a grip force which picks up the micro device from the carrier substrate.

# MICRO DEVICE TRANSFER HEAD HEATER ASSEMBLY AND METHOD OF TRANSFERRING A MICRO DEVICE

## **BACKGROUND**

### **RELATED APPLICATIONS**

[0001] This application claims the benefit of priority from U.S. Provisional Patent Application Serial No. 61/561,706 filed on November 18, 2011, U.S. Provisional Patent Application Serial No. 61/594,919 filed on February 3, 2012, U.S. Provisional Patent Application Serial No. 61/597,109 filed on February 9, 2012 and U.S. Provisional Patent Application Serial No. 61/597,658 filed on February 10, 2012, the full disclosures of which are incorporated herein by reference.

### **FIELD**

**[0002]** The present invention relates to micro devices. More particularly embodiments of the present invention relate to a method of transferring one or more micro devices to a receiving substrate with a micro device transfer head.

### **BACKGROUND INFORMATION**

[0003] Integration and packaging issues are one of the main obstacles for the commercialization of micro devices such as radio frequency (RF) microelectromechanical systems (MEMS) microswitches, light-emitting diode (LED) display systems, and MEMS or quartz-based oscillators.

[0004] Traditional technologies for transferring of devices include transfer by wafer bonding from a transfer wafer to a receiving wafer. One such implementation is "direct printing" involving one bonding step of an array of devices from a transfer wafer to a receiving wafer, followed by removal of the transfer wafer. Another such implementation is "transfer printing" involving two bonding/de-bonding steps. In transfer printing a transfer wafer may pick up an array of devices from a donor wafer, and then bond the array of devices to a receiving wafer, followed by removal of the transfer wafer.

**[0005]** Some printing process variations have been developed where a device can be selectively bonded and de-bonded during the transfer process. In both traditional and variations of the direct printing and transfer printing technologies, the transfer wafer is de-bonded from a device after bonding the device to the receiving wafer. In addition, the entire transfer wafer with the array of devices is involved in the transfer process.

### **SUMMARY OF THE INVENTION**

[0006] A micro device transfer head and head array, and a method of transferring one or more micro devices to a receiving substrate are disclosed. For example, the receiving substrate may be, but is not limited to, a display substrate, a lighting substrate, a substrate with functional devices such as transistors or integrated circuits (ICs), or a substrate with metal redistribution lines.

[0007] In an embodiment, a micro device transfer head includes a base substrate, a mesa structure including sidewalls, at least one is electrode formed over the mesa structure, and a dielectric layer covering the electrode. For example, the micro device transfer head can incorporate a monopolar or bipolar electrode structure. The mesa structure can be separately or integrally formed with the base substrate. The sidewalls can be tapered and protrude away from the base substrate to a top surface of the mesa structure, with the electrode formed on the top surface. An electrode lead may extend from the electrode in order to make contact with wiring in the base substrate and connect the micro device transfer head to the working electronics of an electrostatic gripper assembly. The electrode leads can run from the electrode on the top surface of the mesa structure and along a sidewall of the mesa structure. The electrode lead can alternatively run underneath the mesa structure and connect to a via running through the mesa structure to the electrode.

**[0008]** The electrode and electrode leads may be covered with a deposited dielectric layer. Suitable materials for the dielectric layer include, but are not limited to, aluminum oxide  $(AI_2O_3)$  and tantalum oxide  $(Ta_2O_5)$ . Since the dielectric layer is deposited, the electrode and electrode leads may be formed of a material which can withstand high deposition temperatures, including high melting temperature metals

such as platinum and refractory metals or refractory metal alloys such as titanium tungsten (TiW).

[0009] In an embodiment, a method of transferring a micro device includes positioning a transfer head over a micro device connected to a carrier substrate. The micro device is contacted with the transfer head and a voltage is applied to an electrode in the transfer head to create a grip pressure on the micro device. The transfer head picks up the micro device and then releases the micro device onto a receiving substrate. The voltage can be applied to the electrode prior to, while or after contacting the micro device with the transfer head. The voltage can be a constant current voltage, or alternating current voltage. In an embodiment, an alternating current voltage is applied to a bipolar electrode structure. In an embodiment, an operation is additionally performed to create a phase change in a bonding layer connecting the micro device to the carrier substrate prior to or while picking up the micro device.

[0010] In an embodiment, the bonding layer is heated to create a phase change from solid to liquid in the bonding layer prior to or while picking up the micro device. Depending upon the operating conditions, a substantial portion of the bonding layer can be picked up and transferred with the micro device. A variety of operations can be performed to control the phase of the portion of the bonding layer when picking up, transferring, contacting the receiving substrate, and releasing the micro device and portion of the bonding layer on the receiving substrate. For example, the portion of the bonding layer which is picked up with the micro device can be maintained in the liquid state when contacting the receiving substrate and during the release operation onto the receiving substrate. In another embodiment, the portion of the bonding layer can be allowed to cool to a solid phase after being pick up. For example, the portion of the bonding layer can be in a solid phase prior to or during contacting the receiving substrate, and again melted to the liquid state during the release operation. A variety of temperature and material phase cycles can be performed in accordance with embodiments of the invention.

[0011] In an embodiment, a method of transferring an array of micro devices includes positioning an array of transfer heads over an array of micro devices. The array of micro devices is contacted with the array of transfer heads, and a voltage is

selectively applied to a portion of the array of transfer heads. Selectively applying a voltage may include applying a voltage to all of the transfer heads in the array, or to a portion corresponding to less than all of the transfer heads in the array. The corresponding portion of the array of micro devices is then picked up with the portion of the array of transfer heads, and the portion of the array of micro devices is selectively released onto at least one receiving substrate. In an embodiment, the array of transfer heads may be rubbed on the array of micro devices while making contact in order to dislodge any particles which may be present on the contacting surface of either of the transfer heads or micro devices. In an embodiment, a phase change is created in an array of laterally separate locations of the bonding layer connecting the array of micro devices to the carrier substrate prior to picking up the array of micro devices.

[0012] In an embodiment, a method of fabricating a micro device transfer head array includes forming an array of mesa structures on a base substrate, with each mesa structure including sidewalls. A separate electrode is formed over each mesa structure, and a dielectric layer is deposited over the array of mesa structures and each electrode. In an embodiment, the dielectric layer is deposited with atomic layer deposition (ALD), and may be pin-hole free. The dielectric layer may include one or multiple dielectric layers. A conformal passivation layer may optionally be grown or deposited over the base substrate and the array of mesa structures prior to forming the separate electrode over each corresponding mesa structure. In an embodiment, a conductive ground plane is formed over the dielectric layer and surrounding each of the mesa structures.

[0013] In an embodiment, a method of transferring a micro device includes heating a carrier substrate carrying a micro device connected to a bonding layer to a temperature below a liquidus temperature of the bonding layer, and heating a transfer head to a temperature above the liquidus temperature of the bonding layer. The micro device is contacted with the transfer head and heat transfers from the transfer head into the bonding layer to at least partially melt the bonding layer. A voltage is applied to the transfer head to create a grip pressure on the micro device, and the micro device is picked up with the transfer head. The micro device can then

be placed in contact with and released onto a receiving substrate. The receiving substrate may be globally or locally heated to assist with the transfer process. [0014] In an embodiment, a method of transferring an array of micro devices includes heating a substrate carrying an array of micro devices connected to a plurality of locations of a bonding layer to a temperature below a liquidus temperature of the bonding layer, and heating an array of transfer heads to a temperature above the liquidus temperature of the bonding layer. The array of micro devices are contacted with the array of transfer heads and heat is transferred from the array of transfer heads into the plurality of locations of the bonding layer to at least partially melt portions of the plurality of locations of the bonding layer. A voltage is selectively applied to a portion of the array of transfer heads, and a corresponding portion of the array of micro devices is picked up with the portion of the array of transfer heads. The portion of the array of micro devices can then be placed in contact with and selectively released onto at least one receiving substrate. The receiving substrate may be globally or locally heated to assist with the transfer process.

[0015] In an embodiment, the micro device and array of micro devices are micro LED devices, each including a micro p-n diode and a metallization layer, with the metallization layer between the micro p-n diode and a bonding layer formed on a substrate. When picking up the micro LED device and array of micro LED devices may include picking up the micro p-n diode, the metallization layer and a portion of the bonding layer. A conformal dielectric barrier layer may span sidewalls of the micro p-n diode and a bottom surface of the micro p-n diode. The conformal dielectric barrier layer may be cleaved below the bottom surface of the micro p-n diode.

# BRIEF DESCRIPTION OF THE DRAWINGS

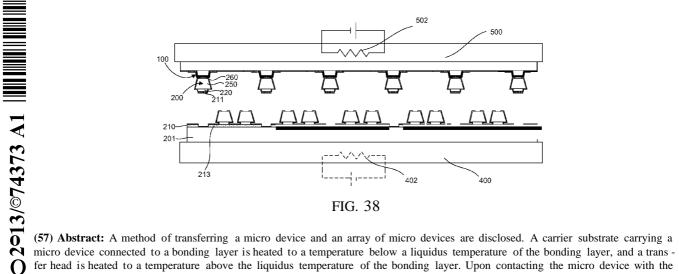

[0016] FIG. 1 is a graphical illustration showing the pressure required to overcome the force of surface tension to pick up a micro device of various dimensions in accordance with an embodiment of the invention.

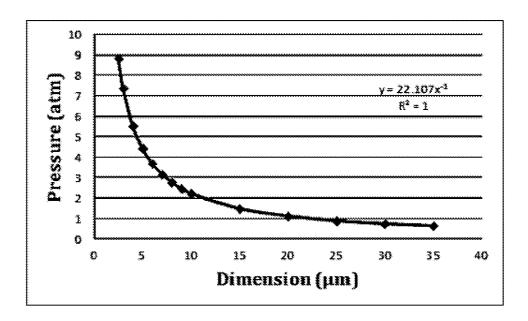

[0017] FIG. 2 is a graphical illustration of the relationship between surface tension and increasing gap distance created during a pick up operation in accordance with an embodiment of the invention.

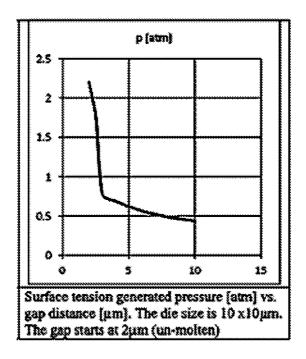

- **[0018]** FIG. 3 is a graphical illustration of the relationship between viscous force pressures and increasing gap distance created during a pick up operation at various pull rates in accordance with an embodiment of the invention.

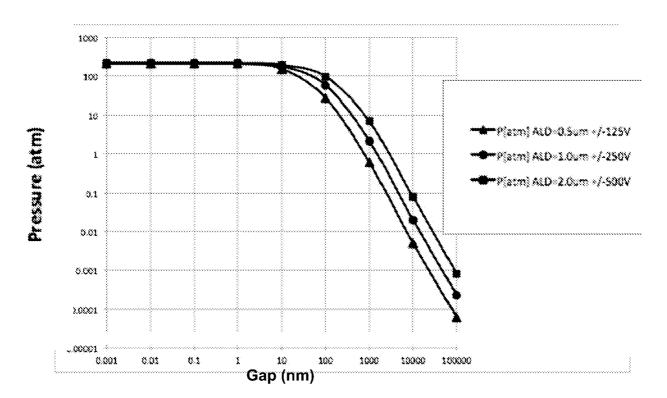

- [0019] FIG. 4 is a graphical illustration obtained by modeling analysis showing the grip pressure exerted by a transfer head on a micro device as the transfer head is withdrawn from the micro device in accordance with an embodiment of the invention.

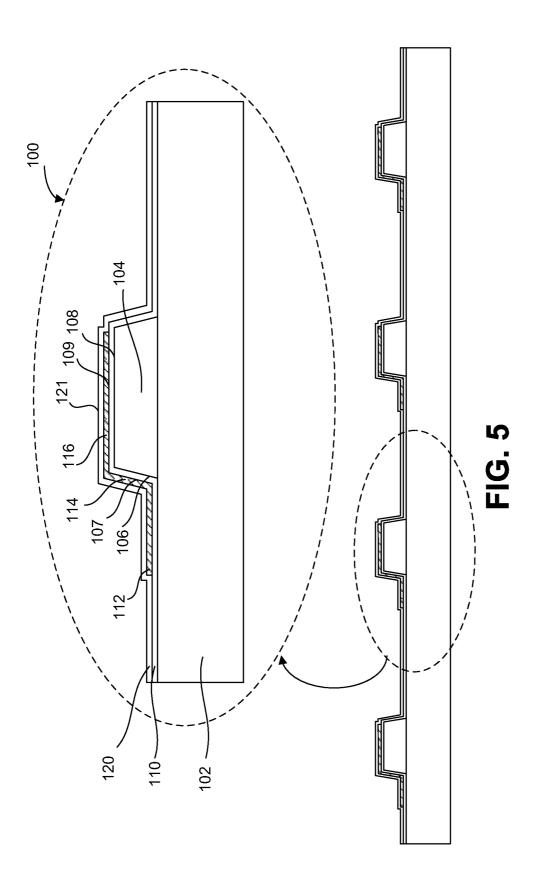

- [0020] FIG. 5 is a cross-sectional side view illustration of a monopolar micro device transfer head in accordance with an embodiment of the invention.

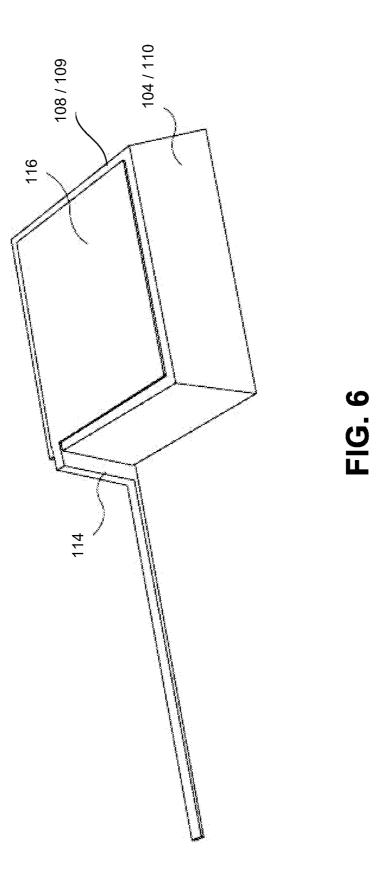

- [0021] FIG. 6 is an isometric view illustration of a monopolar micro device transfer head in accordance with an embodiment of the invention.

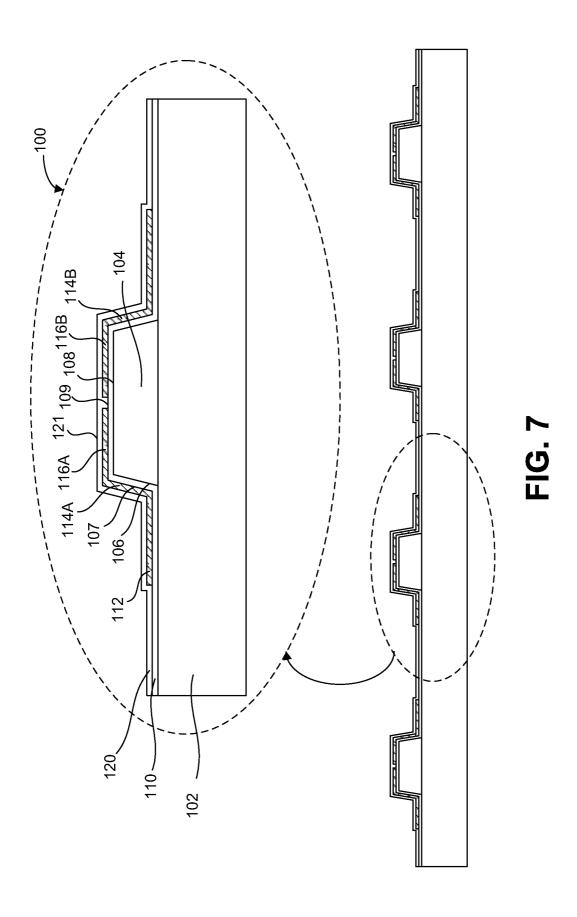

- [0022] FIG. 7 is a cross-sectional side view illustration of a bipolar micro device transfer head in accordance with an embodiment of the invention.

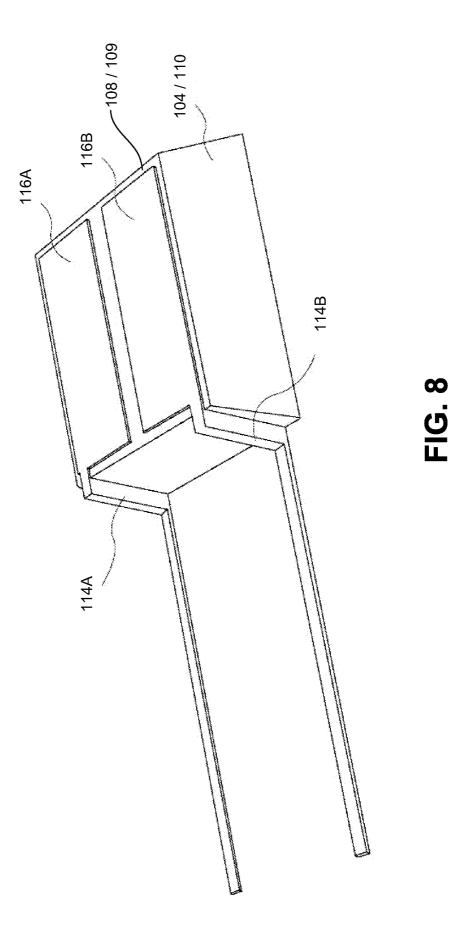

- [0023] FIG. 8 is an isometric view illustration of a bipolar micro device transfer head in accordance with an embodiment of the invention.

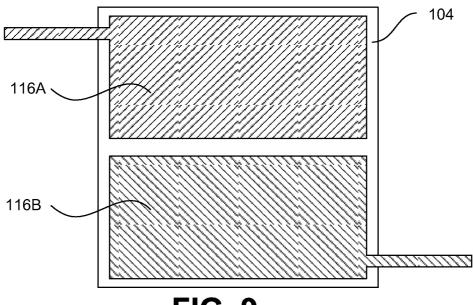

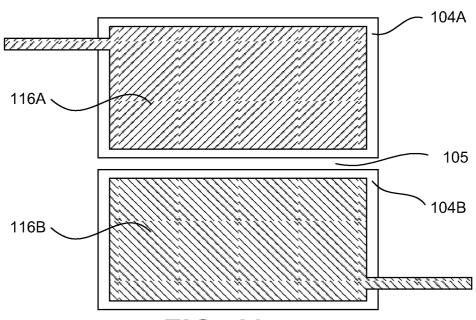

- [0024] FIGS. 9-10 are top view illustrations of bipolar micro device transfer heads in accordance with an embodiment of the invention.

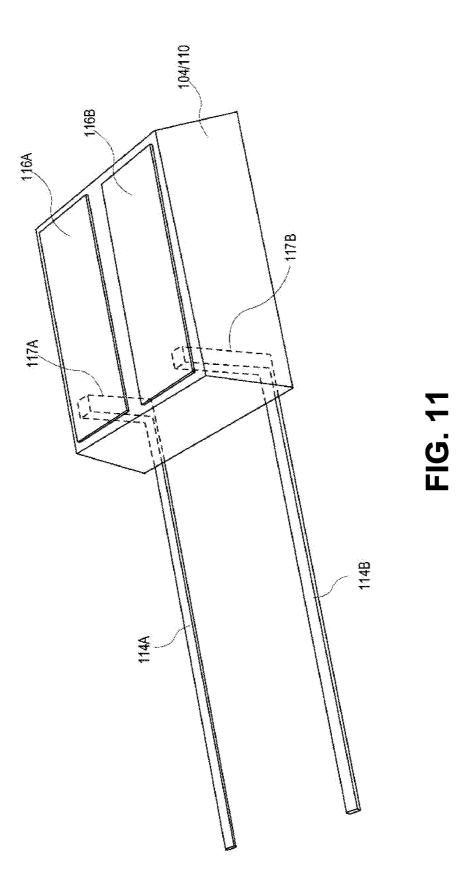

- [0025] FIG. 11 is an isometric view illustration of a bipolar micro device transfer head including conductive vias in accordance with an embodiment of the invention.

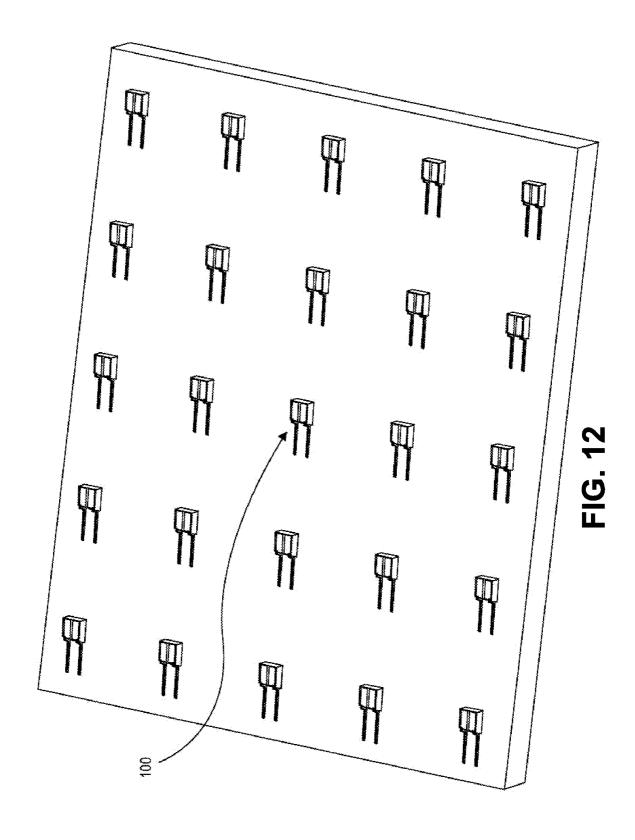

- [0026] FIG. 12 is an isometric view illustration of a bipolar micro device transfer head array in accordance with an embodiment of the invention.

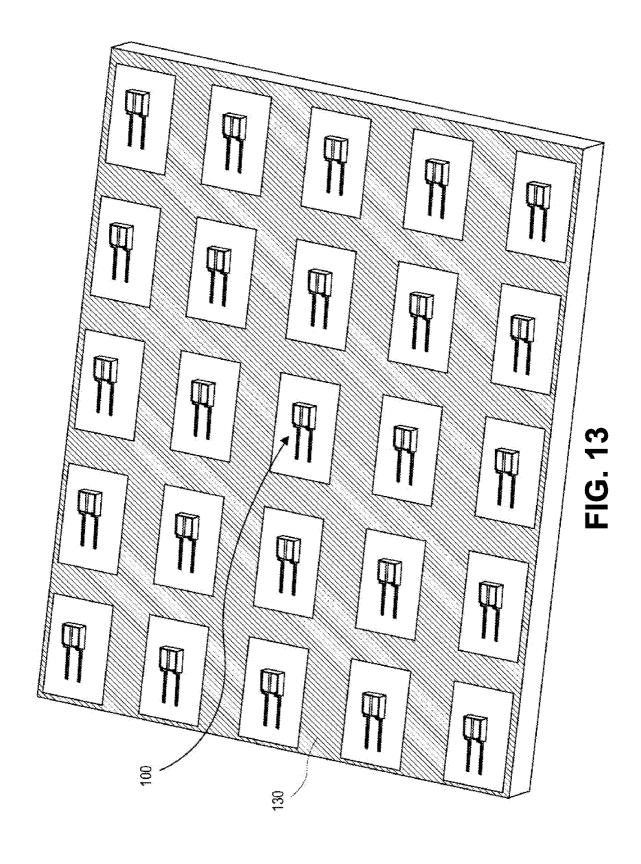

- [0027] FIG. 13 is an isometric view illustration of a bipolar micro device transfer head array including a conductive ground plane in accordance with an embodiment of the invention.

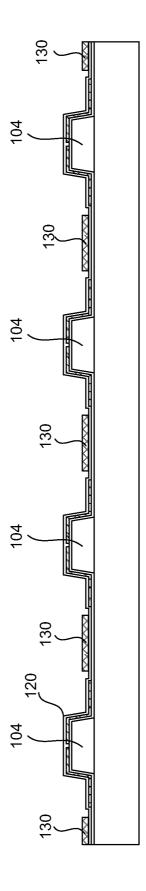

- [0028] FIG. 14 is a cross-sectional side view illustration of a bipolar micro device transfer head array including a conductive ground plane in accordance with an embodiment of the invention.

[0029] FIG. 15 is a flow chart illustrating a method of picking up and transferring a micro device from a carrier substrate to a receiving substrate in accordance with an embodiment of the invention.

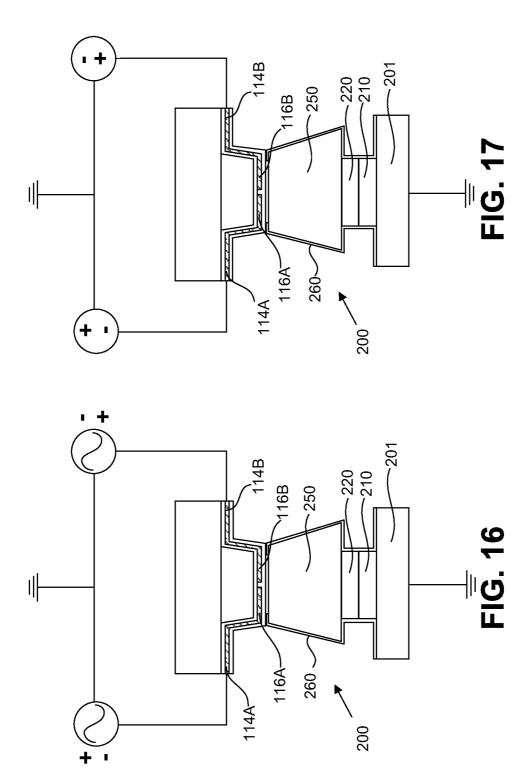

[0030] FIG. 16 is a schematic illustration of an alternating voltage applied across a bipolar electrode in accordance with an embodiment of the invention.

[0031] FIG. 17 is a schematic illustration of a constant voltage applied across a bipolar electrode in accordance with an embodiment of the invention.

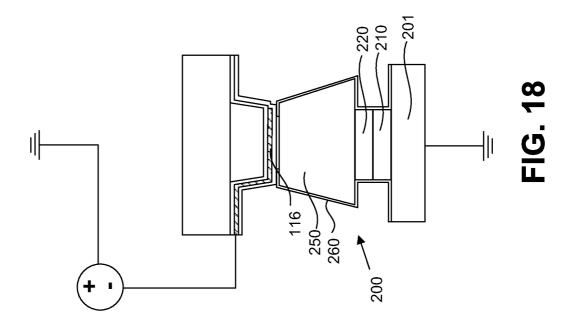

[0032] FIG. 18 is a schematic illustration of a constant voltage applied to a monopolar electrode in accordance with an embodiment of the invention.

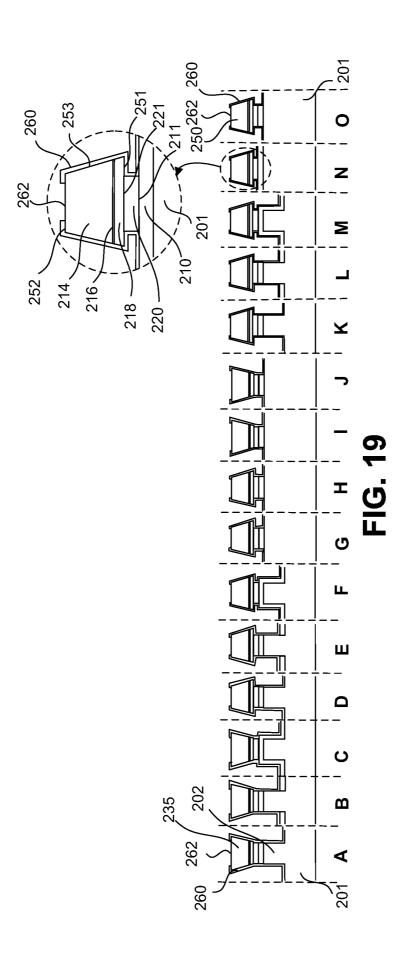

[0033] FIG. 19 is a cross-sectional side view illustration of a variety of micro LED structures including contact openings with a smaller width than the top surface of the micro p-n diode.

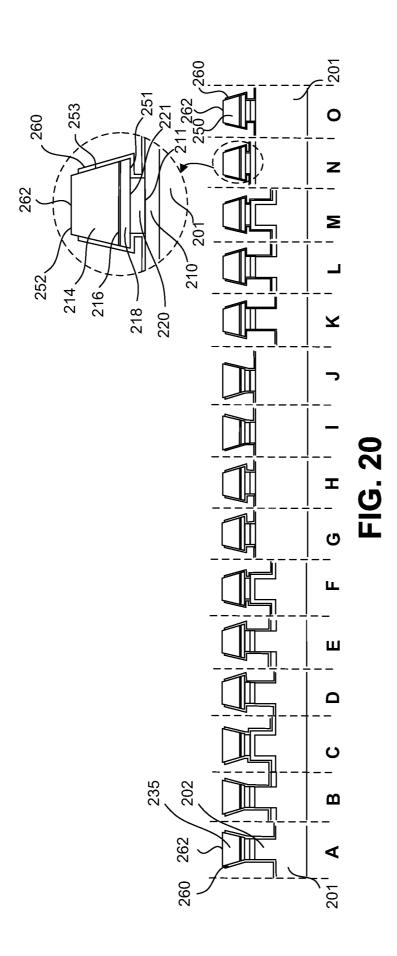

[0034] FIG. 20 is a cross-sectional side view illustration of a variety of micro LED structures including contact openings with a larger width than the top surface of the micro p-n diode.

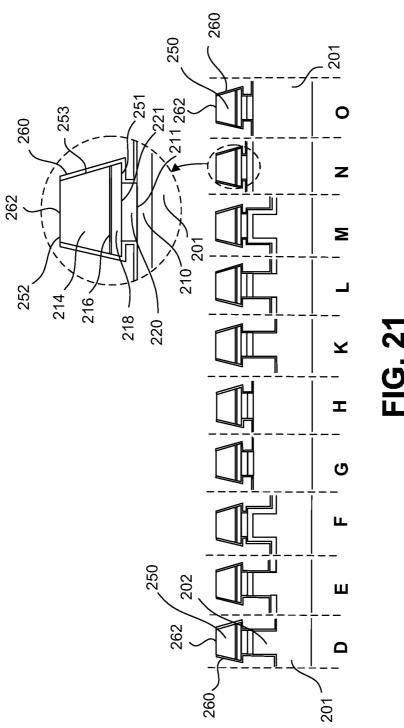

[0035] FIG. 21 is a cross-sectional side view illustration of a variety of micro LED structures including contact openings with the same width as the top surface of the micro p-n diode.

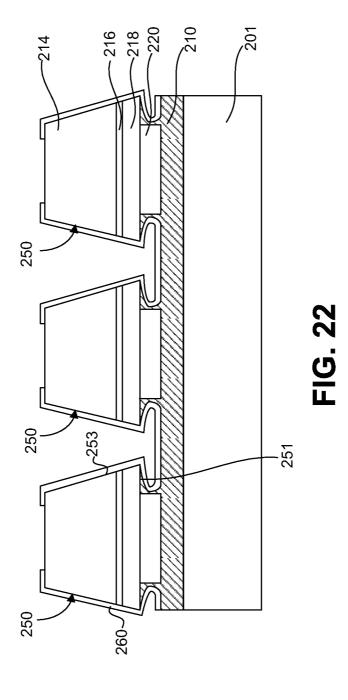

[0036] FIG. 22 is a cross-sectional side view illustration of a wicked up bonding layer in accordance with an embodiment of the invention.

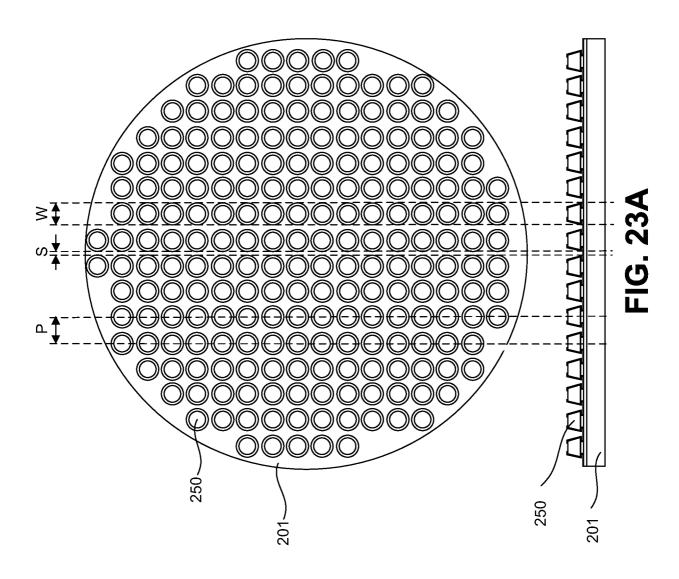

[0037] FIGS. 23A-23B include top and cross-sectional side view illustrations of a carrier wafer and array of micro LED devices in accordance with embodiments of the invention.

[0038] FIG. 24 is a flow chart illustrating a method of picking up and transferring a micro device from a carrier substrate to a receiving substrate in accordance with an embodiment of the invention.

[0039] FIG. 25 is a flow chart illustrating a method of picking up and transferring an array of micro devices from a carrier substrate to at least one receiving substrate in accordance with an embodiment of the invention.

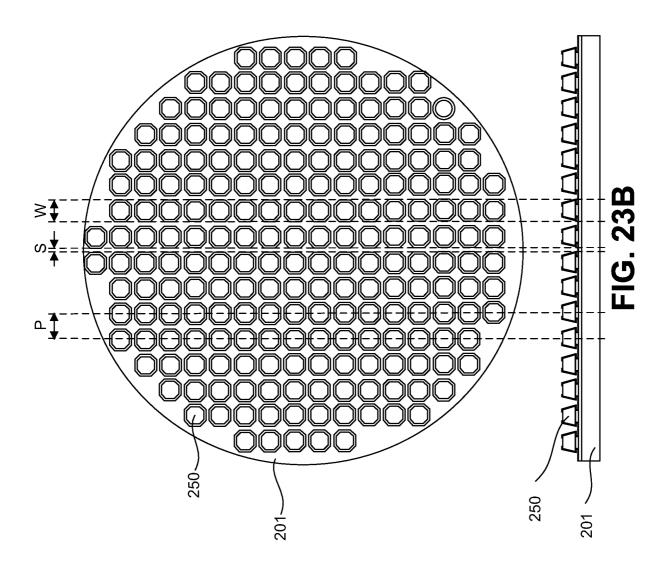

[0040] FIG. 26 is a cross-sectional side view illustration of an array of micro device transfer heads in contact with an array of micro LED devices in accordance with an embodiment of the invention.

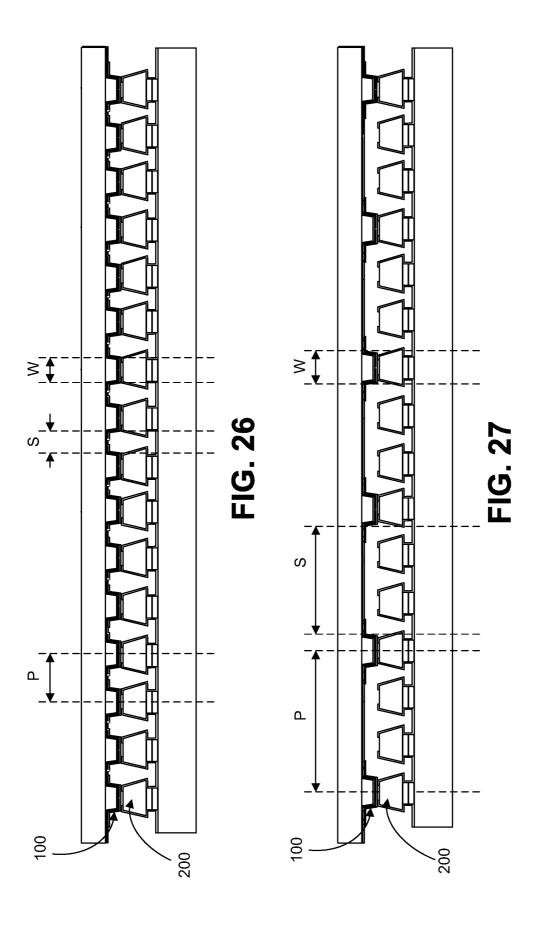

[0041] FIG. 27 is a cross-sectional side view illustration of an array of micro device transfer heads in contact with an array of micro LED devices in accordance with an embodiment of the invention.

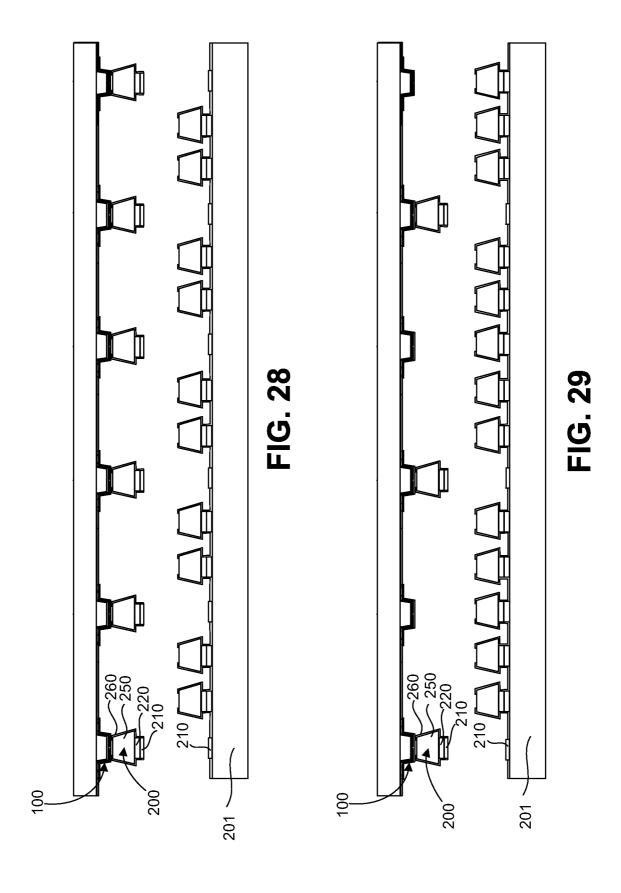

- [0042] FIG. 28 is a cross-sectional side view illustration of an array of micro device transfer heads picking up an array of micro LED devices in accordance with an embodiment of the invention.

- [0043] FIG. 29 is a cross-sectional side view illustration of an array of micro device transfer heads picking up a portion of an array of micro LED devices in accordance with an embodiment of the invention.

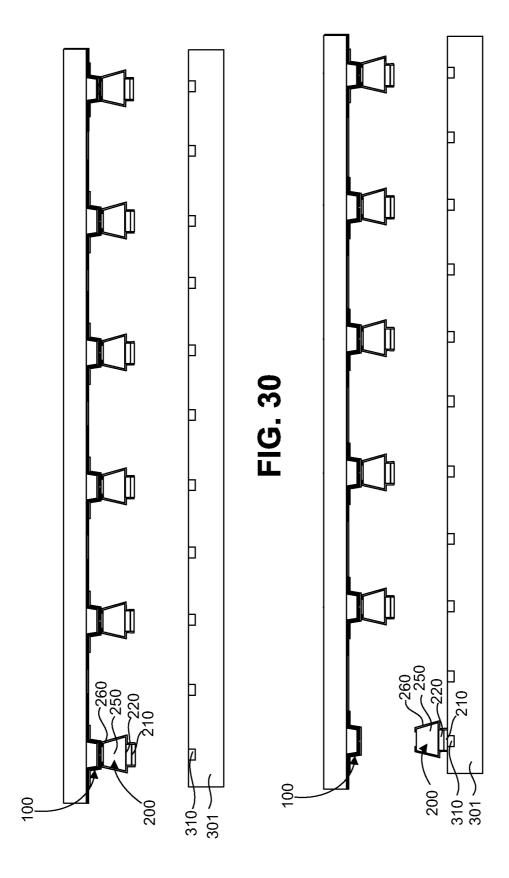

- [0044] FIG. 30 is a cross-sectional side view illustration of an array of micro device transfer heads with an array of micro LED devices positioned over a receiving substrate in accordance with an embodiment of the invention.

- [0045] FIG. 31 is a cross-sectional side view illustration of a micro device selectively released onto a receiving substrate in accordance with an embodiment of the invention.

- [0046] FIG. 32 is a flow chart illustrating a method of picking up and transferring a micro device from a carrier substrate to a receiving substrate in accordance with an embodiment of the invention.

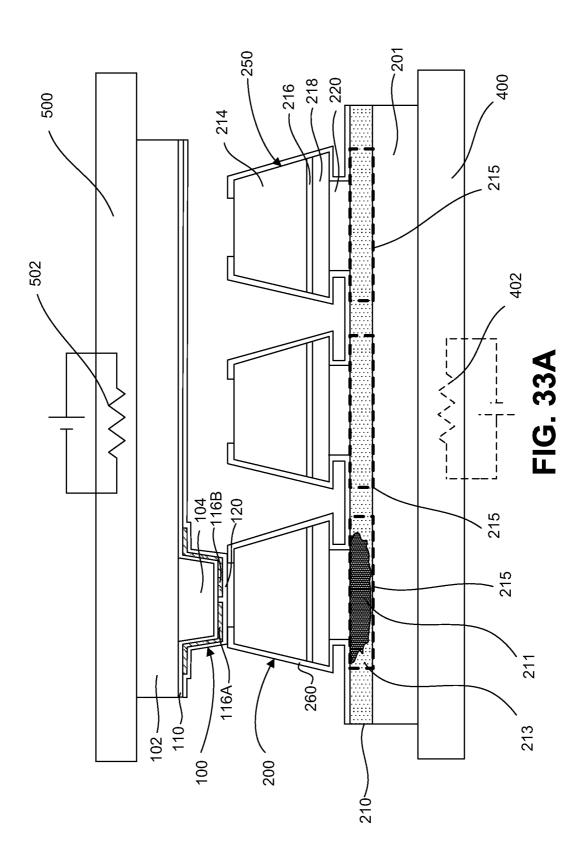

- [0047] FIG. 33A is a cross-sectional side view illustration of an at least partially melted location of a laterally continuous bonding layer in accordance with an embodiment of the invention.

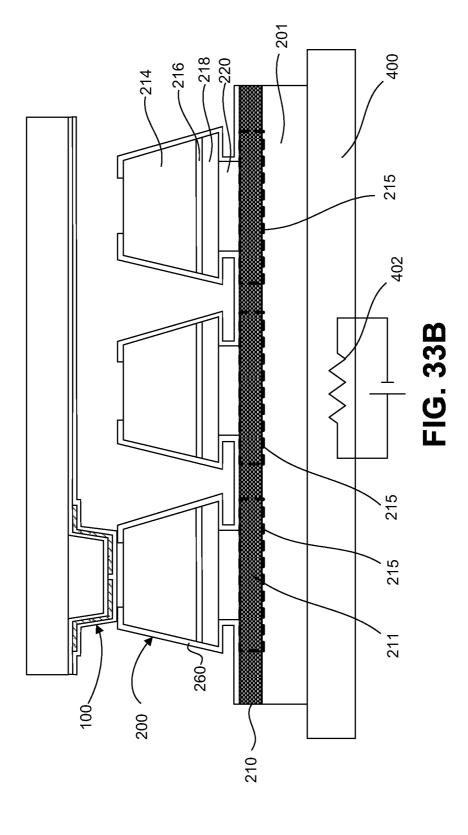

- [0048] FIG. 33B is a cross-sectional side view illustration of at least partially melted locations of a laterally continuous bonding layer in accordance with an embodiment of the invention.

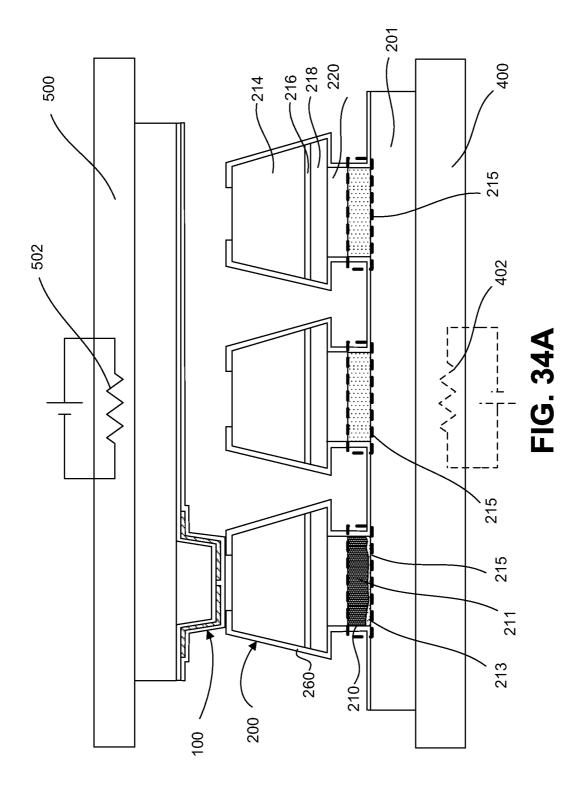

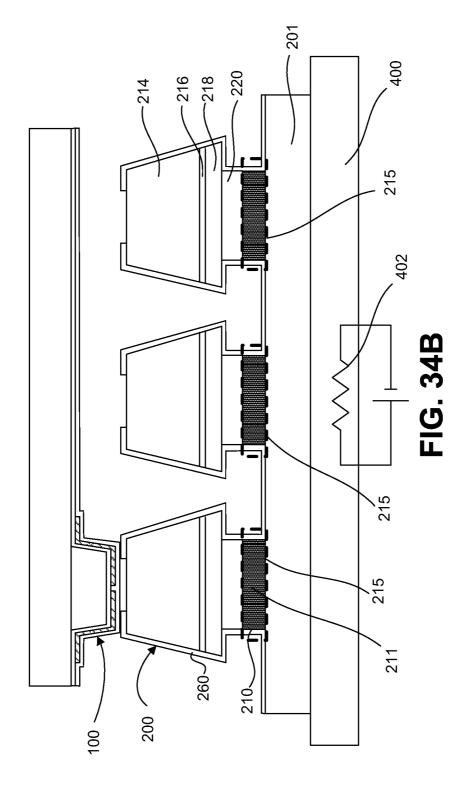

- [0049] FIG. 34A is a cross-sectional side view illustration of an at least partially melted laterally separate location of a bonding layer in accordance with an embodiment of the invention.

- [0050] FIG. 34B is a cross-sectional side view illustration of at least partially melted laterally separate locations of a bonding layer in accordance with an embodiment of the invention.

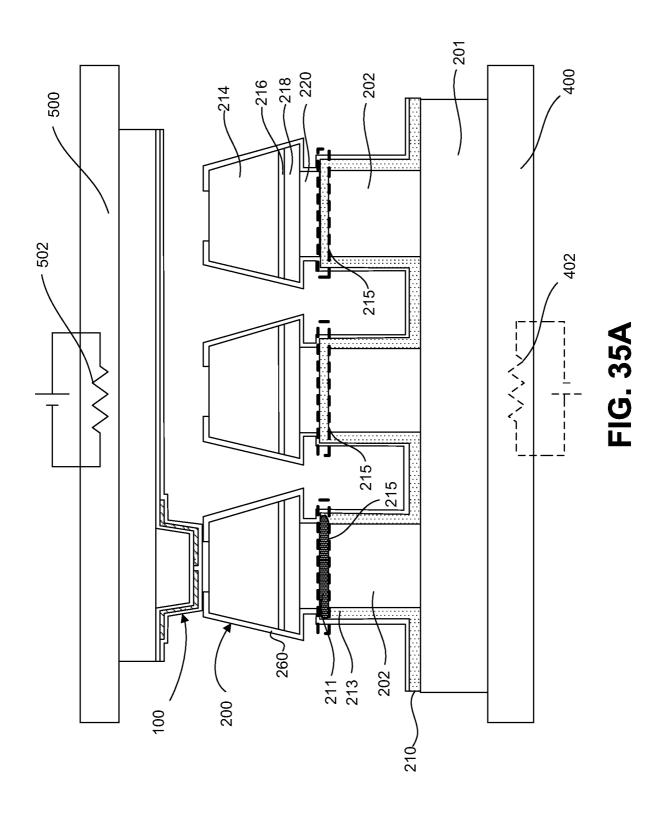

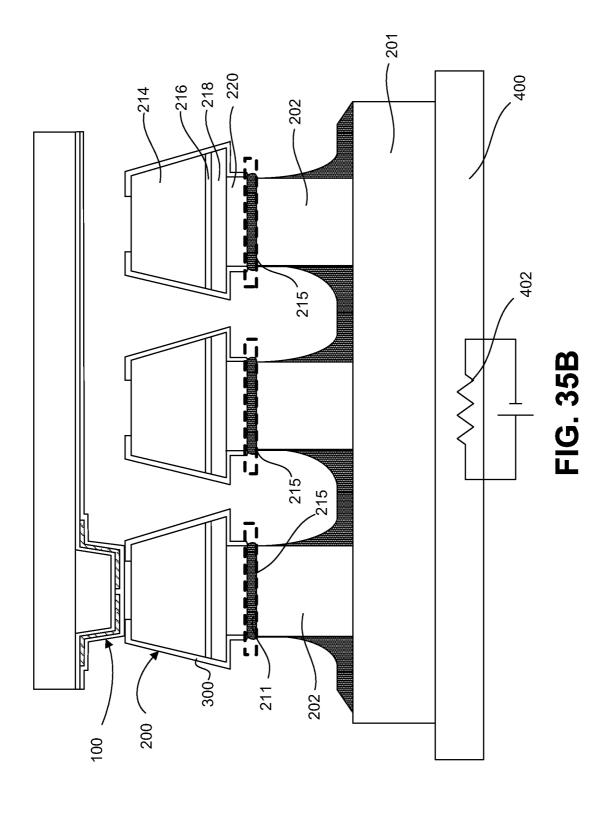

[0051] FIG. 35A is a cross-sectional side view illustration of an at least partially melted laterally separate location of a bonding layer on a post in accordance with an embodiment of the invention.

[0052] FIG. 35B is a cross-sectional side view illustration of at least partially melted laterally separate locations of a bonding layer on posts in accordance with an embodiment of the invention.

[0053] FIG. 36 is a flow chart illustrating a method of picking up and transferring an array of micro devices from a carrier substrate to at least one receiving substrate in accordance with an embodiment of the invention.

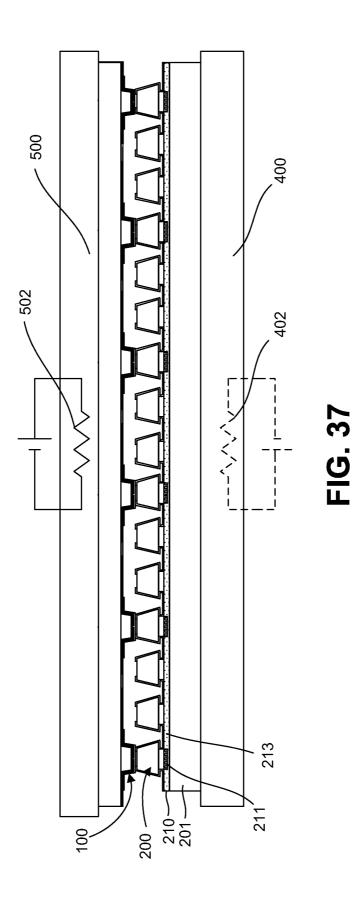

[0054] FIG. 37 is a cross-sectional side view illustration of an array of micro device transfer heads in contact with an array of micro LED devices in accordance with an embodiment of the invention.

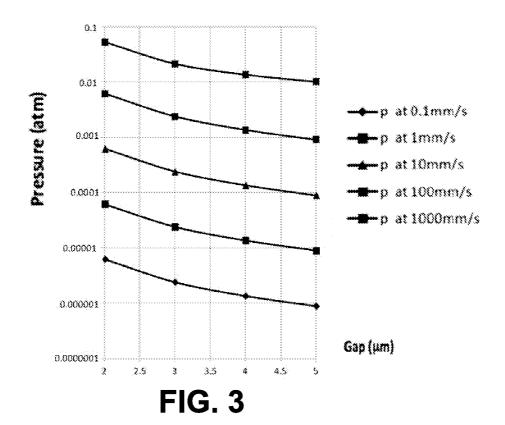

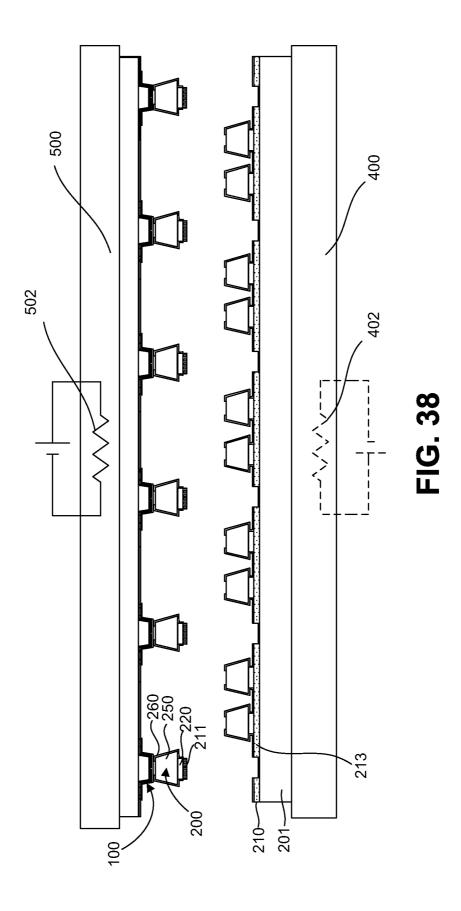

[0055] FIG. 38 is a cross-sectional side view illustration of an array of micro device transfer heads picking up an array of micro LED devices in accordance with an embodiment of the invention.

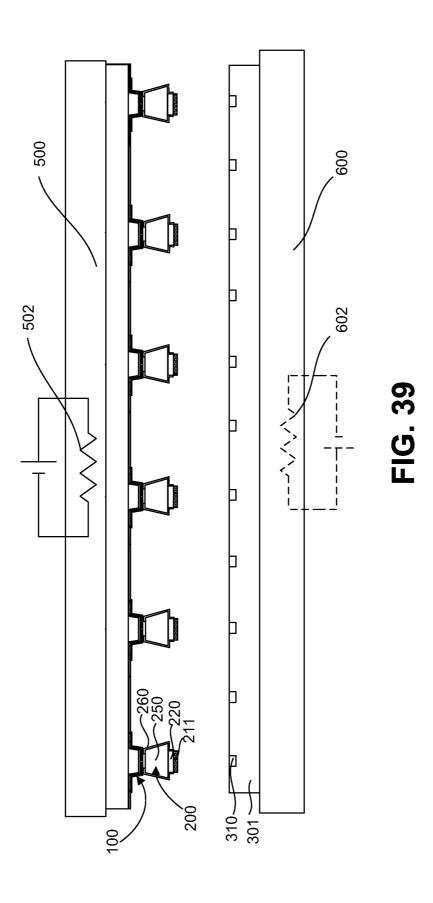

[0056] FIG. 39 is a side view illustration of an array of micro device transfer heads with an array of micro LED devices positioned over a receiving substrate in accordance with an embodiment of the invention.

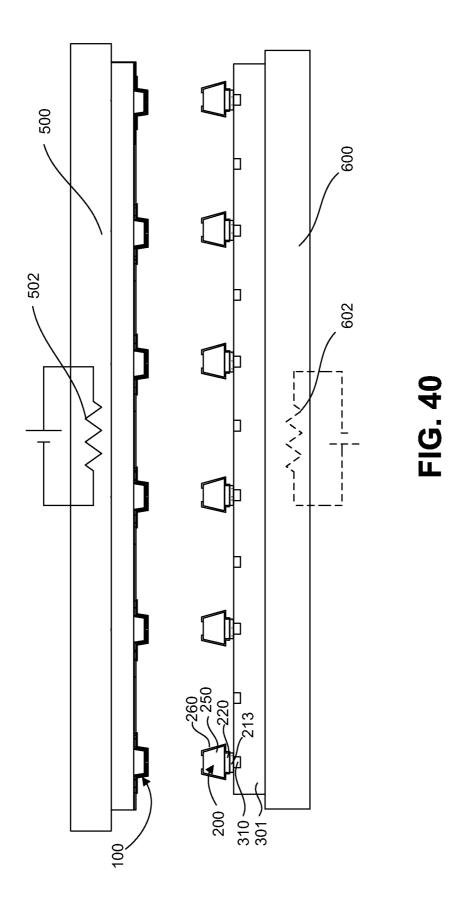

[0057] FIG. 40 is a side view illustration of an array of micro LED devices selectively released onto a receiving substrate in accordance with an embodiment of the invention.

### DETAILED DESCRIPTION OF THE INVENTION

[0058] Embodiments of the present invention describe a micro device transfer head and head array, and method of transferring a micro device and an array of micro devices to a receiving substrate. For example, the receiving substrate may be, but is not limited to, a display substrate, a lighting substrate, a substrate with functional devices such as transistors or integrated circuits (ICs), or a substrate with metal redistribution lines. In some embodiments, the micro devices and array of micro devices described herein may be any of the micro LED device structures illustrated in FIGS. 19-21, and those described in related U.S. Provisional Application No. 61/561,706 and U.S. Provisional Application No. 61/594,919. While some

embodiments of the present invention are described with specific regard to micro LEDs, it is to be appreciated that embodiments of the invention are not so limited and that certain embodiments may also be applicable to other micro devices such as diodes, transistors, ICs, and MEMS.

[0059] In various embodiments, description is made with reference to figures. However, certain embodiments may be practiced without one or more of these specific details, or in combination with other known methods and configurations. In the following description, numerous specific details are set forth, such as specific configurations, dimensions and processes, etc., in order to provide a thorough understanding of the present invention. In other instances, well-known semiconductor processes and manufacturing techniques have not been described in particular detail in order to not unnecessarily obscure the present invention. Reference throughout this specification to "one embodiment," "an embodiment" or the like means that a particular feature, structure, configuration, or characteristic described in connection with the embodiment is included in at least one embodiment of the invention. Thus, the appearances of the phrase "in one embodiment," "an embodiment" or the like in various places throughout this specification are not necessarily referring to the same embodiment of the invention. Furthermore, the particular features, structures, configurations, or characteristics may be combined in any suitable manner in one or more embodiments.

[0060] The terms "over", "to", "between" and "on" as used herein may refer to a relative position of one layer with respect to other layers. One layer "over" or "on" another layer or bonded "to" another layer may be directly in contact with the other layer or may have one or more intervening layers. One layer "between" layers may be directly in contact with the layers or may have one or more intervening layers. [0061] The terms "micro" device or "micro" LED structure as used herein may refer to the descriptive size of certain devices or structures in accordance with embodiments of the invention. As used herein, the terms "micro" devices or structures are meant to refer to the scale of 1 to 100  $\mu$ m. However, it is to be appreciated that embodiments of the present invention are not necessarily so limited, and that certain aspects of the embodiments may be applicable to larger, and possibly smaller size scales.

[0062] In one aspect, embodiments of the invention describe a manner for mass transfer of an array of pre-fabricated micro devices with an array of transfer heads. For example, the pre-fabricated micro devices may have a specific functionality such as, but not limited to, a LED for light-emission, silicon IC for logic and memory, and gallium arsenide (GaAs) circuits for radio frequency (RF) communications. In some embodiments, arrays of micro LED devices which are poised for pick up are described as having a 10 μιη by 10 μιη pitch, or 5 μιη by 5 μιη pitch. At these densities a 6 inch substrate, for example, can accommodate approximately 165 million micro LED devices with a 10 μιη by 10 μιη pitch, or approximately 660 million micro LED devices with a 5 um by 5 um pitch. A transfer tool including an array of transfer heads matching an integer multiple of the pitch of the corresponding array of micro LED devices can be used to pick up and transfer the array of micro LED devices to a receiving substrate. In this manner, it is possible to integrate and assemble micro LED devices into heterogeneously integrated systems, including substrates of any size ranging from micro displays to large area displays, and at high transfer rates. For example, a 1 cm by 1 cm array of micro device transfer heads can pick up and transfer more than 100,000 micro devices, with larger arrays of micro device transfer heads being capable of transferring more micro devices. Each transfer head in the array of transfer heads may also be independently controllable, which enables selective pick up and release of the micro devices.

[0063] In one aspect, without being limited to a particular theory, embodiments of the invention describe micro device transfer heads and head arrays which operate in accordance with principles of electrostatic grippers, using the attraction of opposite charges to pick up micro devices. In accordance with embodiments of the present invention, a pull-in voltage is applied to a micro device transfer head in order to generate a grip force on a micro device and pick up the micro device. Grip force is proportional to charged plate area so is calculated as a pressure. According to ideal electrostatic theory, a non-conductive dielectric layer between a monopolar electrode and a conductive substrate yields a grip pressure in Pascal (Pa) in equation (1) of:

$$P = [0/2] [V_r/d]^2 - - (1)$$

where  $_0 = 8.85.10^{-12}$ , V = electrode-substrate voltage in volts (V),  $_r$  = dielectric constant, and d = dielectric thickness in meters (m). With a bipolar gripper using two grip electrodes the voltage (V) in the above equation is half of the voltage between electrodes A and B,  $[V_A - V_B]/2$ . The substrate potential is centered at the average potential,  $[V_A = V_B]/2$ . This average is generally zero with  $V_A = [-V_B]$ . [0064] In another aspect, embodiments of the invention describe a bonding layer which can maintain a micro device on a carrier substrate during certain processing and handling operations, and upon undergoing a phase change provides a medium on which the micro device can be retained yet is also readily releasable from during a pick up operation. For example, the bonding layer may be remeltable or reflowable such that the bonding layer undergoes a phase change from solid to liquid state prior to or during the pick up operation. In the liquid state the bonding layer may retain the micro device in place on a carrier substrate while also providing a medium from which the micro device is readily releasable. Without being limited to a particular theory, in determining the grip pressure which is necessary to pick up the micro device from the carrier substrate the grip pressure should exceed the forces holding the micro device to the carrier substrate, which may include but are not limited to, surface tension forces, capillary forces, viscous effects, elastic restoration forces, van-der-Waals forces, stiction and gravity.

[0065] In accordance with embodiments of the invention, when the dimensions of a micro device are reduced below a certain range, the surface tension forces of the liquid bonding layer holding the micro device to the carrier substrate may become dominant over other forces holding the micro device. FIG. 1 is a graphical illustration of one embodiment obtained by modeling analysis showing the pressure required to overcome the force of surface tension to pick up a micro device of various dimensions, assuming a liquid indium (In) bonding layer with a surface tension of 560 mN/m at the melting temperature of 156.7 °C. For example, referring to FIG. 1 an exemplary 10  $\mu$ m by 10  $\mu$ m wide micro device is retained on a carrier substrate with a surface tension pressure of approximately 2.2 atmospheres (atm) with an indium bonding layer having a liquid surface tension of 560 mN/m at its

melting temperature of 156.7 °C. This is significantly larger than the pressure due to gravity, which is approximately  $1.8 \times 10^{-6}$  atm for an exemplary  $10 \mu \eta \times 10 \mu \eta$  wide x 3  $\mu \eta$  tall piece of gallium nitride (GaN).

[0066] Surface tension pressures and viscous effects may also be dynamic during the pick up operation. FIG. 2 is a graphical illustration of one embodiment obtained by modeling analysis showing the relationship of surface tension and increasing gap distance created during the pick up operation of an exemplary 10 μιη by 10 μιη wide micro device retained on a carrier substrate with a molten indium (In) bonding layer. The gap distance along the x-axis referred to in FIG. 2 is the distance between the bottom of the micro device and the carrier substrate, and starts at 2 μιη corresponding to an un-molten thickness of the In bonding layer. As illustrated in FIG. 2, a surface tension pressure of 2.2 atm along the y-axis is initially overcome by the grip pressure at the beginning of the pick up operation. As the micro device is then lifted from the carrier substrate, the surface tension rapidly falls, with the pressure leveling out as the micro device is lifted further away from the carrier substrate.

[0067] FIG. 3 is a graphical illustration of one embodiment obtained by modeling analysis showing the relationship of viscous force pressures (atm) and increasing gap distance (μιη) created during a pick up operation at various pull rates for an exemplary 10 μιη by 10 μιη micro device retained on a carrier substrate with a molten indium (In) bonding layer. The gap distance referred to in FIG. 3 is the distance between the bottom of the micro device and the carrier substrate, and starts at 2 μιη corresponding to an un-molten thickness of the In bonding layer. As illustrated, viscous force pressures are more apparent during faster lift speeds such as 1,000 mm/s than for slower lift speeds such as 0.1 mm/s. Yet, the pressures generated from the viscous effects using the exemplary lift speeds illustrated in FIG. 3 are significantly less than the surface tension pressure generated and illustrated in FIG. 2 which suggests that surface tension pressure is the dominant pressure which must be overcome by the grip pressure during the pick up operation.

[0068] If an air gap of size (g) is present between the dielectric layer of the micro device transfer head and a top conductive surface of the micro device then the grip pressure in equation (2) is:

$$P = [_{0}/2] [V_{r}/(d+_{r}g)]^{2}$$

---- (2)

[0069] It is contemplated that an air gap can be present due to a variety of sources including, but not limited to, particulate contamination, warpage, and misalignment of either surface of the transfer head or micro device, or the presence of an additional layer on the transfer head or micro device, such as a lip of a conformal dielectric barrier layer around the top conductive surface of a micro device. In a embodiment, a lip of a conformal dielectric barrier layer may create both an air gap where a contact opening is formed and increase the effective thickness of the dielectric layer of the transfer head where the lip is present.

[0070] As seen from equations (1) and (2) above, lower voltages may be utilized where no air gap is present between the micro device transfer head and micro device to be picked up. However, when an air gap is present this presents a series capacitance in which the air capacitance may compete with the dielectric layer capacitance. In order to compensate for the possibility of an air capacitance between any of an array of micro device transfer heads over a corresponding array of micro devices to be picked up, a higher operating voltage, higher dielectric constant for the dielectric material, or thinner dielectric material may be used to maximize the electric field. However, use of a higher electric field has limitations due to possible dielectric breakdown and arcing.

[0071] FIG. 4 is a graphical illustration of one embodiment obtained by modeling analysis showing the grip pressure exerted by a transfer head on a micro device as the transfer head is withdrawn from the top conductive surface of the micro device, corresponding to an increasing air gap size. The different lines correspond to different  $Ta_2O_5$  dielectric layer thicknesses between 0.5  $\mu\eta$  and 2.0  $\mu\eta$  on the transfer head, with the electric field being kept constant. As illustrated, no appreciable effect on grip pressure is observed at these conditions below air gap sizes of approximately 1 nm (0.001  $\mu\eta$ ), and even as high as 10 nm (0.01  $\mu\eta$ ) for some conditions. However, it is to be appreciated that the tolerable air gap can be increased or decreased by changing the conditions. Thus, in accordance with some embodiments of the invention a certain amount of air gap tolerance is possible

during the pick up operation and actual contact with the micro device transfer head and the top conductive surface of the micro device may not be necessary.

[0072] Now assuming that the grip pressure required to pick up the micro device from the carrier substrate should exceed the sum of pressures retaining the micro device on the carrier substrate (as well as any pressure reduction due to air gap) it is possible to derive the interrelationship of operating voltage, dielectric constant and dielectric thickness of the dielectric material in the micro device transfer head by solving the grip pressure equations. For purposes of clarity, assuming that the air gap distance is zero, for a monopolar electrode this becomes:

sqrt

$$(P*2/_{0}) = V_{r}/d$$

---- (3)

**[0073]** Exemplary ranges of calculated dielectric thickness values are provided in Table 1 for desired grip pressures of 2 atm (202650 Pa) and 20 atm (2026500 Pa) for  $AI_2O_3$  and  $Ta_2O_5$  dielectric materials between operating voltages between 25 V and 300 V in order to illustrate the interdependence of grip pressure, voltage, dielectric constant and dielectric thickness in accordance with an embodiment of the invention. The dielectric constants provided are approximate, and it is understood that the values can vary depending upon manner of formation.

Table 1.

| Dielectric | Voltage (V) | Dielectric     | Dielectric   |

|------------|-------------|----------------|--------------|

| Material   |             | constant, r    | thickness, d |

|            |             | (Hz – MHz      | (microns)    |

|            |             | range)         |              |

|            |             |                |              |

|            | Grip pro    | essure = 2 atm |              |

| $Al_2O_3$  | 25          | 9.8            | 1.1          |

| $Al_2O_3$  | 100         | 9.8            | 4.6          |

| $Al_2O_3$  | 300         | 9.8            | 13.7         |

| $Ta_2O_5$  | 25          | 25             | 2.9          |

| $Ta_2O_5$  | 100         | 25             | 11.7         |

| $Ta_2O_5$  | 300         | 25             | 35.0         |

|            |             |                |              |

|            | Grip pre    | ssure = 20 atm |              |

| $Al_2O_3$  | 25          | 9.8            | 0.4          |

| $Al_2O_3$  | 100         | 9.8            | 1.4          |

| A 1 <sub>2</sub> 0 <sub>3</sub> | 300 | 9.8 | 4.3  |

|---------------------------------|-----|-----|------|

| $Ta_2O_5$                       | 25  | 25  | 0.9  |

| $Ta_2O_5$                       | 100 | 25  | 3.7  |

| $Ta_2O_5$                       | 300 | 25  | 11.1 |

[0074] Since the grip pressure is proportional to the inverse square of the dielectric thickness, the calculated dielectric thicknesses in Table 1 represents the maximum thicknesses which can be formed to achieve the necessary grip pressure with the set operating voltage. Thicknesses lower than those provided in Table 1 may result in higher grip pressures at the set operating voltage, however lower thicknesses increase the applied electric field across the dielectric layer which requires that the dielectric material possess a dielectric strength sufficient to withstand the applied electric field without shorting. It is to be appreciated that the grip pressure, voltage, dielectric constant and dielectric thickness values provided in Table 1 are exemplary in nature, and provided in order to provide a foundation for working ranges of the micro device transfer head in accordance with embodiments of the invention. The relationship between grip pressure, voltage, dielectric constant and dielectric thickness values provided in Table 1 has been illustrated in accordance with ideal electrostatic theory, and embodiments of the invention are not limited by such. [0075] Referring now to FIG. 5, a side view illustration is provided of a monopolar micro device transfer head and head array in accordance with an embodiment of the invention. As shown, each monopolar device transfer head 100 may include a base substrate 102, a mesa structure 104 including a top surface 108 and sidewalls 106, an optional passivation layer 110 formed over the mesa structure 104 and including a top surface 109 and sidewalls 107, an electrode 116 formed over the mesa structure 104 (and optional passivation layer 110) and a dielectric layer 120 with a top surface 121 covering the electrode 116. Base substrate 102 may be formed from a variety of materials such as silicon, ceramics and polymers which are capable of providing structural support. In an embodiment, base substrate has a conductivity between 10<sup>3</sup> and 10<sup>18</sup> ohm-cm. Base substrate 102 may additionally include wiring (not shown) to connect the micro device transfer heads 100 to the working electronics of an electrostatic gripper assembly.

[0076] Mesa structure 104 may be formed using suitable processing techniques, and may be formed from the same or different material than base substrate 102. In one embodiment, mesa structure 104 is integrally formed with base substrate 104, for example by using lithographic patterning and etching, or casting techniques. In an embodiment, anisotropic etching techniques can be utilized to form tapered sidewalls 106 for mesa structure 104. In another embodiment, mesa structure 104 may be deposited or grown, and patterned on top of the base substrate 102. In an embodiment, mesa structure 104 is a patterned oxide layer, such as silicon dioxide, formed over a semiconductor substrate, such as silicon.

[0077] In one aspect, the mesa structures 104 generate a profile which protrudes away from the base substrate so as to provide a localized contact point to pick up a specific micro device during a pick up operation. In an embodiment, mesa structures 104 have a height of approximately 1 μιη to 5 μιη, or more specifically approximately 2 μιη. Specific dimensions of the mesa structures 104 may depend upon the specific dimensions of the micro devices to be picked up, as well as the thickness of any layers formed over the mesa structures. In an embodiment, the height, width, and planarity of the array of mesa structures 104 on the base substrate 102 are uniform across the base substrate so that each micro device transfer head 100 is capable of making contact with each corresponding micro device during the pick up operation. In an embodiment, the width across the top surface 121 of each micro device transfer head is slightly larger, approximately the same, or less than the width of the top surface of the each micro device in the corresponding micro device array so that a transfer head does not inadvertently make contact with a micro device adjacent to the intended corresponding micro device during the pick up operation. As described in further detail below, since additional layers 110, 112, 120 may be formed over the mesa structure 104, the width of the mesa structure may account for the thickness of the overlying layers so that the width across the top surface 121 of each micro device transfer head is slightly larger, approximately the same, or less than the width of the top surface of the each micro device in the corresponding micro device array.

[0078] Still referring to FIG. 5, mesa structure 104 has a top surface 108, which may be planar, and sidewalls 106. In an embodiment, sidewalls 106 may be tapered up

to 10 degrees, for example. Tapering the sidewalls 106 may be beneficial in forming the electrodes 116 and electrode leads 114 as described further below. A passivation layer 110 may then be optionally deposited or grown over the base substrate 102 and array of mesa structures 104. Passivation layer 110 can be deposited by a variety of suitable techniques such as chemical vapor deposition (CVD), sputtering, or atomic layer deposition (ALD). In an embodiment, passivation layer 110 may be 0.5 μιη - 2.0 μιη thick oxide such as, but not limited to, silicon oxide (SiO<sub>2</sub>), aluminum oxide (A1<sub>2</sub>O<sub>3</sub>) or tantalum oxide (Ta<sub>2</sub>O<sub>5</sub>). [0079] A conductive layer 112 may then be deposited over the array of mesa structures 104 and optional passivation layer 110, and patterned to form electrodes 116 and electrode leads 114. For example, a lift off technique can be utilized to form the electrodes 116 and electrode leads 114 in which a resist layer is deposited and patterned over the substrate, followed by deposition of a metal layer, and lift off of the resist and portion of the metal layer on the resist leaving behind the desired pattern. Alternatively, metal layer deposition followed by patterning and etching can be performed to achieve the desired pattern. Electrode leads 114 may run from the electrode 116 over the top surface 108 of a mesa structure 104 (and top surface 109 of optional passivation layer 110) and along a sidewall 106 of the mesa structure 104 (and along a sidewall 107 of optional passivation layer 110). Conductive layer 112 used to form the electrodes 116 and electrode leads 114 may be a single layer or multiple layers. A variety of conductive materials including metals, metal alloys, refractory metals, and refractory metal alloys may be employed to form conductive layer 112. In an embodiment, the conductive layer 112 has a thickness up to 5,000 angstroms (0.5 μιη). In an embodiment, the conductive layer 112 includes a high melting temperature metal such as platinum or a refractory metal or refractory metal alloy. For example, conductive layer may include platinum, titanium, vanadium, chromium, zirconium, niobium, molybdenum, ruthenium, rhodium, hafnium, tantalum, tungsten, rhenium, osmium, iridium and alloys thereof. Refractory metals and refractory metal alloys generally exhibit higher resistance to heat and wear than other metals. In an embodiment, conductive layer 112 is an approximately 500 angstrom (0.05 µm) thick titanium tungsten (TiW) refractory metal alloy.

[0080] A dielectric layer 120 is then deposited over the electrodes 116 and other exposed layers on the base substrate 102. In an embodiment, the dielectric layer 120 has a suitable thickness and dielectric constant for achieving the required grip pressure of the micro device transfer head 100, and sufficient dielectric strength to not break down at the operating voltage. The dielectric layer may be a single layer or multiple layers. In an embodiment, the dielectric layer is 0.5 μιη - 2.0 μιη thick, though thickness may be more or less depending upon the specific topography of the transfer head 100 and underlying mesa structure 104. Suitable dielectric materials may include, but are not limited to, aluminum oxide (AI<sub>2</sub>O<sub>3</sub>) and tantalum oxide (Ta<sub>2</sub>Os). Referring back to Table 1 above, embodiments of A 1<sub>2</sub>O<sub>3</sub> dielectric layers with applied electric fields (determined by dividing the voltage by dielectric thickness) of 22 V/ $\mu$ i $\eta$  to 71 V/ $\mu$ i $\eta$  and Ta<sub>2</sub>0 <sub>5</sub> dielectric layers with applied electric fields of 9 V/μιη to 28 V/μιη were provided. In accordance with embodiments of the invention, the dielectric layer 120 possesses a dielectric strength greater than the applied electric field so as to avoid shorting of the transfer head during operation. Dielectric layer 120 can be deposited by a variety of suitable techniques such as chemical vapor deposition (CVD), atomic layer deposition (ALD) and physical vapor deposition (PVD) such as sputtering. Dielectric layer 120 may additionally be annealed following deposition. In one embodiment, the dielectric layer 120 possesses a dielectric strength of at least 400 V/µm. Such a high dielectric strength can allow for the use of a thinner dielectric layer than the calculated thicknesses provided in exemplary Table 1. Techniques such as ALD can be utilized to deposit uniform, conformal, dense, and/or pin-hole free dielectric layers with good dielectric strength. Multiple layers can also be utilized to achieve such a pin-hole free dielectric layer 120. Multiple layers of different dielectric materials may also be utilized to form dielectric layer 120. In an embodiment, the underlying conductive layer 112 includes platinum or a refractory metal or refractory metal alloy possessing a melting temperature above the deposition temperature of the dielectric layer material(s) so as to not be a limiting factor in selecting the deposition temperature of the dielectric layer. In an embodiment, following the deposition of dielectric layer 120 a thin coating (not illustrated) may be formed over the dielectric layer 120 to provide a specific stiction coefficient to add lateral friction and keep the

micro devices from being knocked off the transfer head during the pick up operation. In such an embodiment, the additional thin coating replaces top surface 121 as the contacting surface, and this surface retains the dimensional array requirements described herein. Furthermore, the additional coating can affect the dielectric properties of the micro device transfer head which may affect the operability of the micro device transfer head. In an embodiment, the additional coating thickness can be minimal (e.g. below 10 nm) so as to have little to no appreciable effect on the grip pressure.

[0081] FIG. 6 is a close-up isometric view of electrode 116 and electrode lead 114 formed over an optional passivation layer 110 covering a mesa structure 104. For purposes of clarity, the overlying dielectric layer 120 is not illustrated, and the optional passivation layer 110 and mesa structure 104 are illustrated as a single mesa structure/passivation layer 104/1 10. In an exemplary embodiment, where the passivation layer 110 and dielectric layer 120 are both 0.5 µm thick, the top surface 108/109 of the mesa structure/passivation layer 104/110 onto which the electrode 116 is formed is approximately 7 μιη x 7 μιη in order to achieve a 8 μιη x 8 μιη top surface of the transfer head 100. In accordance with an embodiment, the electrode 116 covers the maximum amount of surface area of the top surface 108/109 of the mesa structure/passivation layer 104/110 as possible while remaining within patterning tolerances. Minimizing the amount of free space increases the capacitance, and resultant grip pressure which can be achieved by the micro device transfer head. While a certain amount of free space is illustrated on the top surface 108/109 of the mesa structure/passivation layer 104/110 in FIG. 6, the electrode 116 may cover the entire top surface 108/109. The electrode 116 may also be slightly larger than the top surface 108/109, and partially extend down the sidewalls 106/107 of the mesa structure/passivation layer 104/1 10 to ensure complete coverage of the top surface 108/109. It is to be appreciated that the mesa array may have a variety of different pitches, and that embodiments of the invention are not limited to the exemplary 7 μιη x 7 μιη top surface of the mesa structure/passivation layer 104/1 10 in a 10 μιη pitch.

[0082] Referring now to FIG. 7, a side view illustration is provided of a bipolar micro device transfer head 100 and head array in accordance with an embodiment of

the invention. As shown, the bipolar device transfer head 100 may include a base substrate 102, a mesa structure 104 including a top surface 108 and sidewalls 106, passivation layer 110 including a top surface 109 and sidewalls 107, a pair of electrodes 116A, 116B and electrode leads 114A, 114B formed over the mesa structure 104, optional passivation layer 110 and a dielectric layer 120 covering the pair of electrodes 116A, 116B.

[0083] FIG. 8 is a close-up isometric view of electrodes 116A, 116B and electrode leads 114A, 114B formed over an optional passivation layer 110 covering a mesa structure 104. For purposes of clarity, the overlying dielectric layer 120 is not illustrated, and the optional passivation layer 110 and mesa structure 104 are illustrated as a single mesa structure/passivation layer 104/110. FIG. 8 differs slightly from FIG. 7 in that the electrode leads 114A, 114B are illustrated as running along a single sidewall rather than on opposite sidewalls of the mesa structure/passivation layer 104/110. Electrode leads 114A, 114B may run along any suitable sidewall in accordance with embodiments of the invention. In an exemplary embodiment, where the top surface 108/109 of the mesa structure/passivation layer 104/1 10 is approximately 7 μιη x 7 μιη corresponding to a mesa array with a 10 μιη pitch the electrodes may cover the maximum amount of the surface area of the top surface 108/109 of the mesa structure/passivation layer 104/110 as possible while still providing separation between electrodes 116A, 116B. The minimum amount of separation distance may be balanced by considerations for maximizing surface area, while avoiding overlapping electric fields from the electrodes. For example, the electrodes 116A, 116B may be separated by 0.5 µm or less, and the minimum separation distance may be limited by the height of the electrodes. In an embodiment, the electrodes are slightly longer than the top surface 108/109 in one direction, and partially extend down the sidewalls of the mesa structure/passivation layer 104/1 10 to ensure maximum coverage of the top surface 108/109. It is to be appreciated that the mesa array may have a variety of different pitches, and that embodiments of the invention are not limited to the exemplary 7 μιη x 7 μιη top surface of the mesa structure/passivation layer 104/1 10 in a 10 μιη pitch. [0084] Referring now to FIGS. 9-10, top view illustrations of electrodes 116A,

116B of a bipolar micro device transfer head are provided in accordance with

embodiments of the invention. Thus far, mesa structure 104 has been described as a single mesa structure as shown in FIG. 9. However, embodiments of the invention are not so limited. In the embodiment illustrated in FIG. 10, each electrode 116 is formed on a separate mesa structure 104A, 104B separated by a trench 105. An optional passivation layer 110 (not illustrated) can cover both mesa structures 104A, 104B.

[0085] Referring now to FIG. 11, an isometric view illustration of an alternative electrode lead configuration is provided in accordance with an embodiment of the invention. In such an embodiment the electrode leads 114A, 114B run underneath a portion of the mesa structure 104, and conductive vias 117A, 117B run through the mesa structure 104 (and optional passivation layer 110 not illustrated) connecting the electrodes 116A, 116B to the respective electrode leads 114A, 114B. In such an embodiment, electrode leads 114A, 114B may be formed prior to formation of mesa structure 104, and may be formed of the same or different conductive material as electrode leads 114A, 114B and electrodes 116A, 116B. While vias 117A, 117B are illustrated with regard to a bipolar electrode structure in FIG. 11 it is to be appreciated that the above described via or vias may also be integrated into monopolar electrode structures.

[0086] Referring now to FIGS. 12-14, an embodiment of the invention is illustrated in which a conductive ground plane is formed over the dielectric layer and surrounding the array of mesa structures. FIG. 12 is an isometric view illustration of an array of micro device transfer heads 100 with a bipolar electrode configuration as previously described with regard to FIG. 8. For purposes of clarity, the optional underlying passivation layer and overlying dielectric layer have not been illustrated. Referring now to FIGS. 13-14, a conductive ground plane 130 is formed over the dielectric layer 120 and surrounding the array of mesa structures 104. The presence of ground plane 130 may assist in the prevention of arcing between transfer heads 100, particularly during the application of high voltages. Ground plane 130 may be formed of a conductive material which may be the same as, or different as the conductive material used to form the electrodes, or vias. Ground plane 130 may also be formed of a conductive material having a lower melting temperature than the conductive material used to form the electrodes since it is not necessary to deposit a

dielectric layer of comparable quality (e.g. dielectric strength) to dielectric layer 120 after the formation of ground plane 130.

[0087] FIG. 15 is a flow chart illustrating a method of picking up and transferring a micro device from a carrier substrate to a receiving substrate in accordance with an embodiment of the invention. At operation 1510 a transfer head is positioned over a micro device connected to a carrier substrate. The transfer head may comprise a mesa structure, an electrode over the mesa structure, and a dielectric layer covering the electrode as described in the above embodiments. Thus, the transfer head may have a monopolor or bipolar electrode configuration, as well as any other structural variations as described in the above embodiments. The micro device is then contacted with the transfer head at operation 1520. In an embodiment, the micro device is contacted with the dielectric layer 120 of the transfer head. In an alternative embodiment, the transfer head is positioned over the micro device with a suitable air gap separating them which does not significantly affect the grip pressure, for example, 1 nm  $(0.001 \mu \eta)$  or 10 nm  $(0.01 \mu \eta)$ . At operation 1530 a voltage is applied to the electrode to create a grip pressure on the micro device, and the micro device is picked up with the transfer head at operation 1540. The micro device is then released onto a receiving substrate at operation 1550.

**[0088]** While operations 1510 - 1550 have been illustrated sequentially in FIG. 15, it is to be appreciated that embodiments are not so limited and that additional operations may be performed and certain operations may be performed in a different sequence. For example, in one embodiment, after contacting the micro device with the transfer head, the transfer head is rubbed across a top surface of the micro device in order to dislodge any particles which may be present on the contacting surface of either of the transfer head or micro device. In another embodiment, an operation is performed to create a phase change in the bonding layer connecting the micro device to the carrier substrate prior to or while picking up the micro device. If a portion of the bonding layer is picked up with the micro device, additional operations can be performed to control the phase of the portion of the bonding layer during subsequent processing.

[0089] Operation 1530 of applying the voltage to the electrode to create a grip pressure on the micro device can be performed in various orders. For example, the

voltage can be applied prior to contacting the micro device with the transfer head, while contacting the micro device with the transfer head, or after contacting the micro device with the transfer head. The voltage may also be applied prior to, while, or after creating the phase change in the bonding layer.

[0090] FIG. 16 is a schematic illustration of an alternating voltage applied across a bipolar electrode with the transfer head in contact with a micro device in accordance with an embodiment of the invention. As illustrated, a separate alternating current (AC) voltage source may be applied to each electrode lead 114A, 114B with an alternating voltage applied across the pair of electrodes 116A, 116B so that at a particular point in time when a negative voltage is applied to electrode 116A, a positive voltage is applied to electrode 116B, and vice versa. Releasing the micro device from the transfer head may be accomplished with a variety of methods including turning off the voltage sources, lowering the voltage across the pair of electrodes, changing a waveform of the AC voltage, and grounding the voltage source. FIG. 17 is a schematic illustration of a constant voltage applied to a bipolar electrode in accordance with an embodiment of the invention. In the particular embodiment illustrated, a negative voltage is applied to electrode 116A while a positive voltage is applied to electrode 116B. FIG. 18 is a schematic illustration of a constant voltage applied to a monopolar electrode in accordance with an embodiment of the invention. Once the transfer head picks up the micro device illustrated in FIG. 18, the amount of time the transfer head can hold the micro device may be a function of the discharge rate of the dielectric layer since only single voltage is applied to electrode 116. Releasing the micro device from the transfer head illustrated in FIG. 14 may be accomplished by turning off the voltage source, grounding the voltage source, or reversing the polarity of the constant voltage. [0091] In the particular embodiments illustrated in FIGS. 16-18, the micro devices 200 are those illustrated in FIG. 19, Example 190. Though the micro devices illustrated in FIGS. 16-18 may be from any of the micro LED device structures illustrated in FIGS. 19 -21, and those described in related U.S. Provisional Application No. 61/561,706 and U.S. Provisional Application No. 61/594,919. For example, a micro LED device 200 may include a micro p-n diode 235, 250 and a metallization layer 220, with the metallization layer between the micro p-n diode

235, 250 and a bonding layer 210 formed on a substrate 201. In an embodiment, the micro p-n diode 250 includes a top n-doped layer 214, one or more quantum well layers 216, and a lower p-doped layer 218. The micro p-n diodes can be fabricated with straight sidewalls or tapered sidewalls. In certain embodiments, the micro p-n diodes 250 possess outwardly tapered sidewalls 253 (from top to bottom). In certain embodiments, the micro p-n diodes 235 possess inwardly tapered sidewalls 253 (from top to bottom). The metallization layer 220 may include one or more layers. For example, the metallization layer 220 may include an electrode layer and a barrier layer between the electrode layer and the bonding layer. The micro p-n diode and metallization layer may each have a top surface, a bottom surface and sidewalls. In an embodiment, the bottom surface 251 of the micro p-n diode 250 is wider than the top surface 252 of the micro p-n diode, and the sidewalls 253 are tapered outwardly from top to bottom. The top surface of the micro p-n diode 235 may be wider than the bottom surface of the p-n diode, or approximately the same width. In an embodiment, the bottom surface 251 of the micro p-n diode 250 is wider than the top surface 221 of the metallization layer 220. The bottom surface of the micro p-n diode may also be wider than the top surface of the metallization layer, or approximately the same width as the top surface of the metallization layer. [0092] A conformal dielectric barrier layer 260 may optionally be formed over the micro p-n diode 235, 250 and other exposed surfaces. The conformal dielectric barrier layer 260 may be thinner than the micro p-n diode 235, 250, metallization layer 220 and optionally the bonding layer 210 so that the conformal dielectric barrier layer 260 forms an outline of the topography it is formed on. In an embodiment, the micro p-n diode 235, 250 is several microns thick, such as 3 μιη, the metallization layer 220 is 0.1 μιη - 2 μιη thick, and the bonding layer 210 is 0.1 μιη - 2 μιη thick. In an embodiment, the conformal dielectric barrier layer 260 is approximately 50 - 600 angstroms thick aluminum oxide (AI<sub>2</sub>O<sub>3</sub>). Conformal dielectric barrier layer 260 may be deposited by a variety of suitable techniques such as, but not limited to, atomic layer deposition (ALD). The conformal dielectric barrier layer 260 may protect against charge arcing between adjacent micro p-n diodes during the pick up process, and thereby protect against adjacent micro p-n diodes from sticking together during the pick up process. The conformal dielectric

barrier layer 260 may also protect the sidewalls 253, quantum well layer 216 and bottom surface 251, of the micro p-n diodes from contamination which could affect the integrity of the micro p-n diodes. For example, the conformal dielectric barrier layer 260 can function as a physical barrier to wicking of the bonding layer material 210 up the sidewalls and quantum layer 216 of the micro p-n diodes 150. The conformal dielectric barrier layer 260 may also insulate the micro p-n diodes 250 once placed on a receiving substrate. In an embodiment, the conformal dielectric barrier layer 260 span sidewalls 253 of the micro p-n diode, and may cover a quantum well layer 216 in the micro p-n diode. The conformal dielectric barrier layer may also partially span the bottom surface 251 of the micro p-n diode, as well as span sidewalls of the metallization layer 220. In some embodiments, the conformal dielectric barrier layer also spans sidewalls of a patterned bonding layer 210. A contact opening 262 may be formed in the conformal dielectric barrier layer 260 exposing the top surface 252 of the micro p-n diode. In an embodiment, conformal dielectric barrier layer 260 is formed of the same material as dielectric layer 120 of the bonding head. Depending upon the particular micro LED device structure, the conformal dielectric barrier layer 260 may also span sidewalls of the bonding layer 210, as well as the carrier substrate and posts, if present. [0093] Referring to FIG. 19, the contact opening 262 may have a smaller width than the top surface 252 of the micro p-n diode and the conformal dielectric barrier layer 260 forms a lip around the edges of the top surface 252 of the micro p-n diode. Referring to FIG. 20, the contact opening 262 may have a slightly larger width than the top surface of the micro p-n diode. In such an embodiment, the contact opening 302 exposes the top surface 252 of the micro p-n diode and an upper portion of the sidewalls 253 of the micro p-n diode, while the conformal dielectric barrier layer 260 covers and insulates the quantum well layer(s) 216. Referring to FIG. 21, the conformal dielectric layer 260 may have approximately the same width as the top surface of the micro p-n diode. The conformal dielectric layer 260 may also span along a bottom surface 251 of the micro p-n diodes illustrated in FIGS. 19-21. [0094] Bonding layer 210 may be formed from a material which can maintain the micro LED device 200 on the carrier substrate 201 during certain processing and handling operations, and upon undergoing a phase change provide a medium on

which the micro LED device 200 can be retained yet also be readily releasable from during a pick up operation. For example, the bonding layer may be remeltable or reflowable such that the bonding layer undergoes a phase change from solid to liquid state prior to or during the pick up operation. In the liquid state the bonding layer may retain the micro LED device in place on the carrier substrate while also providing a medium from which the micro LED device 200 is readily releasable. In an embodiment, the bonding layer 210 has a liquidus temperature or melting temperature below approximately 350 °C, or more specifically below approximately 200 °C. At such temperatures the bonding layer may undergo a phase change without substantially affecting the other components of the micro LED device. For example, the bonding layer may be formed of a metal or metal alloy, or a thermoplastic polymer which is removable. For example, the bonding layer may include indium, tin or a thermoplastic polymer such as polyethylene or polypropylene. In an embodiment, the bonding layer may be conductive. For example, where the bonding layer undergoes a phase change from solid to liquid in response to a change in temperature a portion of the bonding layer may remain on the micro LED device during the pick up operation. In such an embodiment, it may be beneficial that the bonding layer is formed of a conductive material so that it does not adversely affect the micro LED device when it is subsequently transferred to a receiving substrate. In this case, the portion of conductive bonding layer remaining on the micro LED device during the transfer may aid in bonding the micro LED device to a conductive pad on a receiving substrate. In a specific embodiment, the bonding layer may be formed of indium, which has a melting temperature of 156.7 °C. The bonding layer may be laterally continuous across the substrate 201, or may also be formed in laterally separate locations. For example, a laterally separate location of the bonding layer may have a width which is less than or approximately the same width as the bottom surface of the micro p-n diode or metallization layer. In some embodiments, the micro p-n diodes may optionally be formed on posts 202 on the substrate.

[0095] Solders may be suitable materials for bonding layer 210 since many are generally ductile materials in their solid state and exhibit favorable wetting with semiconductor and metal surfaces. A typical alloy melts not a single temperature,

but over a temperature range. Thus, solder alloys are often characterized by a liquidus temperature corresponding to the lowest temperature at which the alloy remains liquid, and a solidus temperature corresponding to the highest temperature at which the alloy remains solid. An exemplary list of low melting solder materials which may be utilized with embodiments of the invention are provided in Table 1.

Table 1.

| Chemical composition | Liquidus Temperature (°C) | Solidus Temperature |

|----------------------|---------------------------|---------------------|

|                      |                           | (°C)                |

| 100 In               | 156.7                     | 156.7               |

| 66.3In33.7Bi         | 72                        | 72                  |

| 51In32.5Bi16.5Sn     | 60                        | 60                  |

| 57Bi26In17Sn         | 79                        | 79                  |

| 54.02Bi29.68In16.3Sn | 81                        | 81                  |

| 67Bi33In             | 109                       | 109                 |

| 50In50Sn             | 125                       | 118                 |

| 52Sn48In             | 131                       | 118                 |

| 58Bi42Sn             | 138                       | 138                 |

| 97In3Ag              | 143                       | 143                 |

| 58Sn42In             | 145                       | 118                 |

| 99.3In0.7Ga          | 150                       | 150                 |

| 95In5Bi              | 150                       | 125                 |

| 99.4In0.6Ga          | 152                       | 152                 |

| 99.6In0.4Ga          | 153                       | 153                 |

| 99.5In0.5Ga          | 154                       | 154                 |

| 60Sn40Bi             | 170                       | 138                 |

| 100Sn                | 232                       | 232                 |

| 95Sn5Sb              | 240                       | 235                 |

[0096] An exemplary list thermoplastic polymers which may be utilized with embodiments of the invention are provided in Table 2.

Table 2.

| Polymer                          | Melting Temperature (°C) |

|----------------------------------|--------------------------|

| Acrylic (PMMA)                   | 130–140                  |

| Polyoxymethylene (POM or Acetal) | 166                      |

| Polybutylene terephthalate (PBT) | 160                      |

| Polycaprolactone (PCL)           | 62                       |

| Polyethylene terephthalate (PET) | 260                      |

| Polycarbonate (PC)             | 267     |

|--------------------------------|---------|

| Polyester_                     | 260     |

| Polyethylene (PE)              | 105-130 |

| Polyetheretherketone (PEEK)    | 343     |

| Polylactic acid (PLA)          | 50-80   |

| Polypropylene (PP)             | 160     |

| Polystyrene (PS)               | 240     |

| Polyvinylidene chloride (PVDC) | 185     |

[0097] Referring now to FIG. 22, in accordance with some embodiments it is possible that an amount of bonding layer wicked up along the side surfaces of the metallization layer 220 and along the bottom surface 251 of the micro p-n diode 250 during fabrication of the array of micro p-n diodes 250 on the carrier substrate 201. In this manner, conformal dielectric barrier layer 260 spanning along the bottom surface 251 of the micro p-n diodes 250 and side surfaces of the metallization layers 220 may function as a physical barrier to protect the sidewalls 253 and quantum well layer 216 of the micro p-n diodes 250 from contamination by the bonding layer material 210 during subsequent temperature cycles (particularly at temperatures above the liquidus or melting temperature of the bonding layer material 210) such as during picking up the micro LED devices from the carrier substrate, and releasing the micro LED devices onto the receiving substrate.

[0098] FIGS. 23A-23B include top and cross-sectional side view illustrations of a carrier substrate 201 and array of micro LED devices in accordance with an embodiment of the invention. In the particular embodiments illustrated, the arrays are produced from micro LED devices of Example 19N including micro p-n diode 150. However, it is to be appreciated that FIGS. 23A-23B are meant to be exemplary, and that the array of micro LED devices can be formed from any of the micro LED devices previously described. In the embodiment illustrated in FIG. 23A, each individual micro p-n diode 250 is illustrated as a pair of concentric circles having different diameters or widths corresponding the different widths of the top and bottom surfaces of the micro p-n diode 250, and the corresponding tapered sidewalls spanning between the top and bottom surfaces. In the embodiment illustrated in FIG. 23B, each individual micro p-n diode 250 is illustrated as a pair of concentric squares with tapered or rounded corners, with each square having a

different width corresponding to the different widths of the top and bottom surfaces of the micro p-n diode 250, and the corresponding tapered sidewalls spanning from the top and bottom surfaces. However, embodiments of the invention do not require tapered sidewalls, and the top and bottom surfaces of the micro p-n diode 250 may have the same diameter, or width, and vertical sidewalls. As illustrated in FIGS. 23A-23B the array of micro LED devices is described as having a pitch (P), spacing (S) between each micro LED device and maximum width (W) of each micro LED device. In order for clarity and conciseness, only x-dimensions are illustrated by the dotted lines in the top view illustration, though it is understood that similar ydimensions may exist, and may have the same or different dimensional values. In the particular embodiments illustrated in FIGS. 23A-23B, the x- and y- dimensional values are identical in the top view illustration. In one embodiment, the array of micro LED devices may have a pitch (P) of 10 μιη, with each micro LED device having a spacing (S) of 2 µm and maximum width (W) of 8 µm. In another embodiment, the array of micro LED devices may have a pitch (P) of 5 μιη, with each micro LED device having a spacing (S) of 2 μιη and maximum width (W) of 3 μιη. However, embodiments of the invention are not limited to these specific dimensions, and any suitable dimension may be utilized.

[0099] FIG. 24 is a flow chart illustrating a method of picking up and transferring a micro device from a carrier substrate to a receiving substrate in accordance with an embodiment of the invention. At operation 2410 a transfer head is positioned over a micro device connected to a carrier substrate with a bonding layer. The transfer head may be any transfer head described herein. The micro device may be any of the micro LED device structures illustrated in FIGS. 19-21, and those described in related U.S. Provisional Application No. 61/561,706 and U.S. Provisional Application No. 61/594,919. The micro device is then contacted with the transfer head at operation 2420. In an embodiment, the micro device is contacted with the dielectric layer 120 of the transfer head. In an alternative embodiment, the transfer head is positioned over the micro device with a suitable air gap separating them which does not significantly affect the grip pressure, for example, 1 nm (0.001 μη) or 10 nm (0.01 μη). At operation 2425 an operation is performed to create a phase change in the bonding layer 210 from solid to liquid state. For example, the

operation may include heating an In bonding layer at or above the melting temperature of 156.7 °C. In another embodiment, operation 2425 can be performed prior to operation 2420. At operation 2430 a voltage is applied to the electrode to create a grip pressure on the micro device, and the micro device and a substantial portion of the bonding layer 210 are picked up with the transfer head at operation 2440. For example, approximately half of the bonding layer 210 may be picked up with the micro device. In an alternative embodiment, none of the bonding layer 210 is picked up with the transfer head. At operation 2445 the micro device and portion of the bonding layer 210 are placed in contact with a receiving substrate. The micro device and portion of the bonding layer 210 are then released onto the receiving substrate at operation 2450. A variety of operations can be performed to control the phase of the portion of the bonding layer when picking up, transferring, contacting the receiving substrate, and releasing the micro device and portion of the bonding layer 210 on the receiving substrate. For example, the portion of the bonding layer which is picked up with the micro device can be maintained in the liquid state during the contacting operation 2445 and during the release operation 2450. In another embodiment, the portion of the bonding layer can be allowed to cool to a solid phase after being picked up. For example, the portion of the bonding layer can be in a solid phase during contacting operation 2445, and again melted to the liquid state prior to or during the release operation 2450. A variety of temperature and material phase cycles can be performed in accordance with embodiments of the invention.

[00100] FIG. 25 is a flow chart illustrating a method of picking up and transferring an array of micro devices from a carrier substrate to at least one receiving substrate in accordance with an embodiment of the invention. At operation 2510 an array of transfer heads is positioned over an array of micro devices, with each transfer head having a mesa structure, an electrode over the mesa structure, and a dielectric layer covering the electrode. At operation 2520 the array of micro devices are contacted with the array of transfer heads. In an alternative embodiment, the array of transfer heads is positioned over the array of micro devices with a suitable air gap separating them which does not significantly affect the grip pressure, for example, 1 nm (0.001 μη) or 10 nm (0.01 μη). FIG. 26 is a side view